# Mini PCI Specification

Revision 1.0 October 25, 1999

| REVISION | REVISION HISTORY | DATE     |

|----------|------------------|----------|

| 1.0      | Initial release. | 10/25/99 |

The PCI Special Interest Group disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does the PCI Special Interest Group make a commitment to update the information contained herein.

Contact the PCI Special Interest Group office to obtain the latest revision of the specification.

Questions regarding the Mini PCI specification or membership in the PCI Special Interest Group may be forwarded to:

PCI Special Interest Group 2575 N.E. Kathryn #17 Hillsboro, Oregon 97124

Phone: 800-433-5177 (inside the U.S.)

503-693-6360 (outside the U.S.)

Fax: 503-693-8344 e-mail pcisig@pcisig.com http://www.pcisig.com

#### **DISCLAIMER**

This Mini PCI Specification is provided "as is" with no warranties whatsoever, including any warranty of merchantability, noninfringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample. The PCI SIG disclaims all liability for infringement of proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

Ethernet is a registered trademark of Xerox Corporation.

All other product names are trademarks, registered trademarks, or servicemarks of their respective owners.

Copyright © 1999 PCI Special Interest Group

### **Contents**

### **Chapter 1 Introduction**

| 1.1 | Overview                                                                                 | 1  |

|-----|------------------------------------------------------------------------------------------|----|

| 1.2 | Motivation                                                                               | 1  |

| 1.3 | Features and Benefits                                                                    | 3  |

| 1.4 | Specification References                                                                 | 5  |

| 1.5 | Administration                                                                           | 6  |

| Cha | apter 2 Signal Definition                                                                |    |

| 2.1 | PCI Local Bus Specification References                                                   | 7  |

| 2.2 | System Connector Interface Signals                                                       |    |

| 2.3 | Mini PCI Exceptions and Differences                                                      | 11 |

| 2.4 | System Connector Pinout                                                                  | 13 |

|     | Function-Specific Connectors—Communications Support  5.1 LED Support  5.2 Chassis Ground | 16 |

| Cha | apter 3 Buses                                                                            |    |

| 3.1 | Introduction                                                                             | 17 |

| 3.2 | System Connector                                                                         | 18 |

| 3 3 | Function-Specific Connector                                                              | 19 |

### **Chapter 4 Electrical Specification**

| 4.1        | System Interface Connector                                 | 21 |  |  |  |  |  |

|------------|------------------------------------------------------------|----|--|--|--|--|--|

| 4.         | Audio Interface Modes                                      |    |  |  |  |  |  |

| 4.2        | Mini PCI Function-Specific Connector                       | 24 |  |  |  |  |  |

|            | .2.1 LED Voltage and Current Specifications                |    |  |  |  |  |  |

| 4.         | .2.1 LED Voltage and Current Specifications                |    |  |  |  |  |  |

| 4.3        | Communications Signal Characteristics and EMC              | 25 |  |  |  |  |  |

| 4.         | .3.1 Modem                                                 | 26 |  |  |  |  |  |

| 4.         | .3.2 NIC                                                   | 26 |  |  |  |  |  |

| 4.         | .3.3 Host System                                           | 26 |  |  |  |  |  |

| 4.         | .3.4 Labeling                                              | 27 |  |  |  |  |  |

| 4.         | .3.5 NIC Performance Considerations                        | 27 |  |  |  |  |  |

| 4.4        | PCI Bus Loading                                            | 28 |  |  |  |  |  |

| 4.5        | MPCIACT# Signal                                            | 28 |  |  |  |  |  |

| Cha        | apter 5 Mechanical Specification                           |    |  |  |  |  |  |

| 5.1        | Overview                                                   | 31 |  |  |  |  |  |

|            |                                                            |    |  |  |  |  |  |

| 5.2        | Safety                                                     | 31 |  |  |  |  |  |

| 5.         | .2.1 Modem Safety                                          |    |  |  |  |  |  |

| 5.         | .2.2 NIC Safety                                            |    |  |  |  |  |  |

| 5.         | .2.3 I/O Connector Safety                                  |    |  |  |  |  |  |

| 5.         | .2.4 Host System Safety                                    |    |  |  |  |  |  |

|            | .2.5 Labeling                                              |    |  |  |  |  |  |

| 5.3        | Physical Configuration                                     | 35 |  |  |  |  |  |

| 5.4        | Mechanical Design Details                                  | 36 |  |  |  |  |  |

| 5.4        | .4.1 Type IA Form Factor                                   |    |  |  |  |  |  |

|            | .4.2 Type IB Form Factor                                   |    |  |  |  |  |  |

| 5.4        | .4.3 Type IIA Form Factor                                  |    |  |  |  |  |  |

|            | .4.4 Type IIB Form Factor                                  |    |  |  |  |  |  |

| 5.         | .4.5 Type IIIA Form Factor                                 |    |  |  |  |  |  |

|            | .4.6 Type IIIB Form Factor                                 |    |  |  |  |  |  |

|            | .4.7 Type III PCB Details                                  |    |  |  |  |  |  |

| <i>-</i> - |                                                            |    |  |  |  |  |  |

| 5.5        | Connector Information                                      |    |  |  |  |  |  |

| 5          | .5.1 System Connectors                                     |    |  |  |  |  |  |

|            | 5.5.1.1 Type I and Type II System Connector Specifications |    |  |  |  |  |  |

|            | 5.5.1.2 Type III System Connector Specifications           |    |  |  |  |  |  |

|            | .5.2 Type I and Type III LAN and Modem I/O Connectors      |    |  |  |  |  |  |

| 5          | .5.3 RJ Connectors for Type II Mini PCI Cards              | 61 |  |  |  |  |  |

| 5.6        | Thermal Guidelines                                         | 62 |  |  |  |  |  |

|            |                                                            |    |  |  |  |  |  |

### **Chapter 6 Configuration Space**

| 6.1 | 1 Configuration Space Organization                             | 6                |

|-----|----------------------------------------------------------------|------------------|

| Ch  | Chapter 7 Power Management                                     |                  |

| 7.1 | 1 Power Management for Mini PCI Cards                          | 6                |

| 7   | 7.1.1 3.3VAUX Implementation                                   | 60               |

|     | 7.1.1.1 Industry Specification Definitions and Require         |                  |

|     | 7.1.1.2 D3 <sub>cold</sub> Support                             | 68               |

|     | 7.1.1.2.1 No D3 <sub>cold</sub> Support                        |                  |

|     | 7.1.1.2.2 System Board Supports D3 <sub>cold</sub> Wake Events |                  |

|     | 7.1.1.3 Guidelines For Handling Non-Standard 3.3VA             | UX Transitions69 |

|     | 7.1.1.3.1 3.3VAUX Lost, 3.3V Present                           | 7                |

|     | 7.1.1.3.2 3.3VAUX Lost, 3.3V Not Present                       | 71               |

|     | 7.1.1.3.3 3.3VAUX Transients                                   | 7                |

| 7.2 | 2 Power Consumption                                            | 72               |

| 7 3 | 3 Ontional PCI Implementations Required on Mini PCI Ca         | rds 7            |

# **Figures**

| Figure 1-1: Logical Representation of the Mini PCI Specification                     | 2  |

|--------------------------------------------------------------------------------------|----|

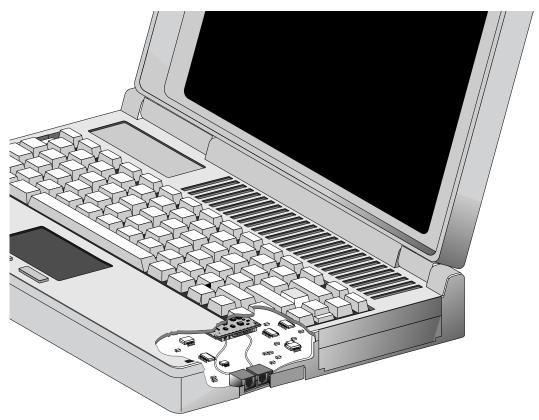

| Figure 1-2: Type I/Type III Mini PCI Card in a Notebook Computer                     | 3  |

| Figure 1-3: Mini PCI and Standard PCI Size Comparison                                | 4  |

| Figure 2-1: Mini PCI Card System PCI Signal Set                                      | 8  |

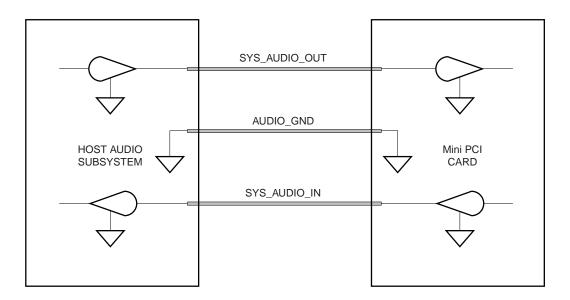

| Figure 4-1: System Audio Implementation for All Types                                | 23 |

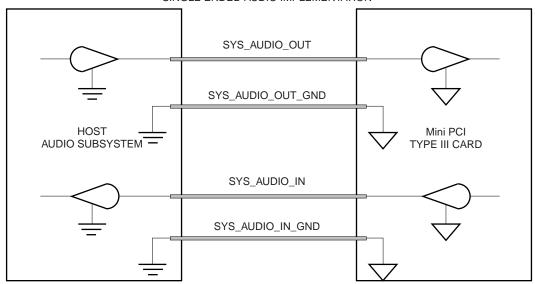

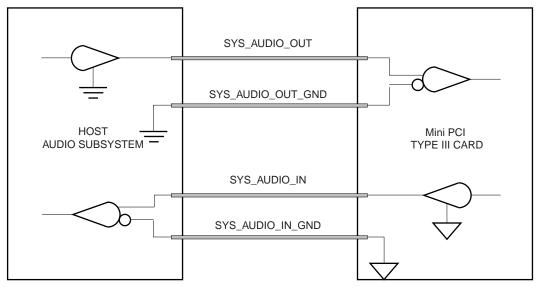

| Figure 4-2: Example of Single Ended and Differential Audio Signals for Type III Only | 24 |

| Figure 5-1: Type I or Type III Mini PCI Card (Sample Installation)                   | 35 |

| Figure 5-2: Type II Mini PCI Card (Sample Installation)                              | 36 |

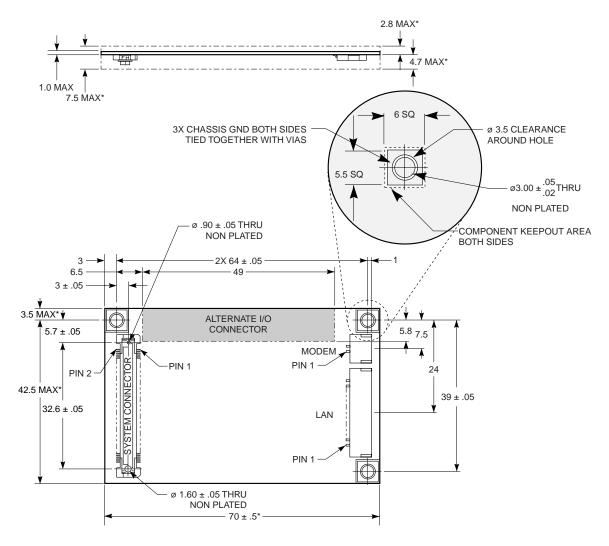

| Figure 5-3: Type IA Form Factor                                                      | 38 |

| Figure 5-4: Type IB Form Factor                                                      | 40 |

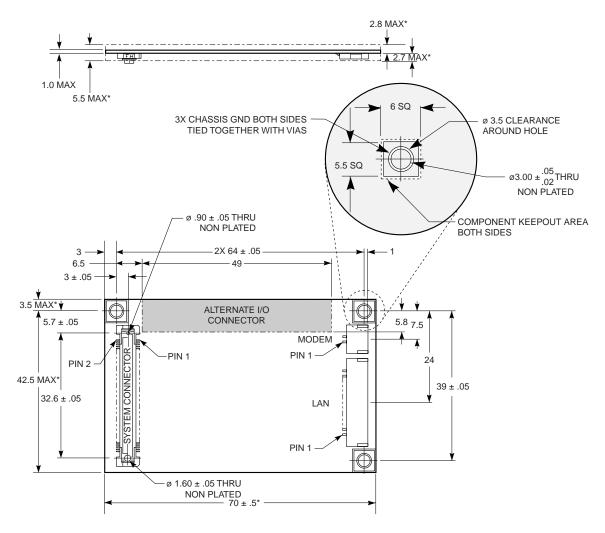

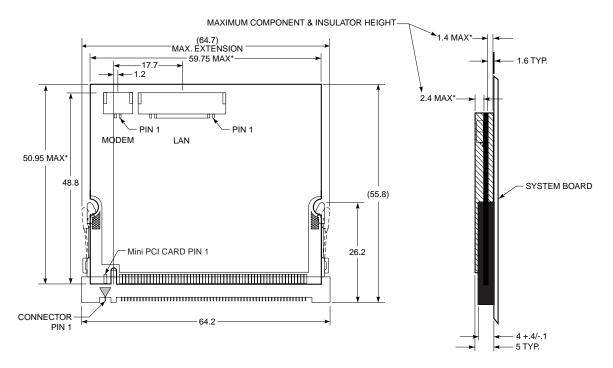

| Figure 5-5: Type IIA Form Factor                                                     | 42 |

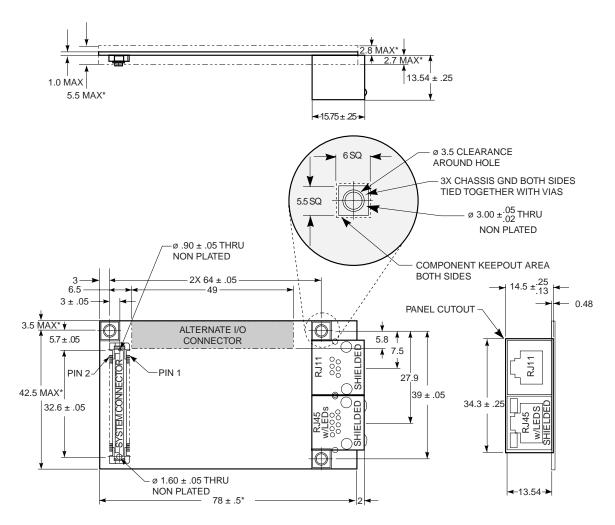

| Figure 5-6: Type IIB Form Factor                                                     | 44 |

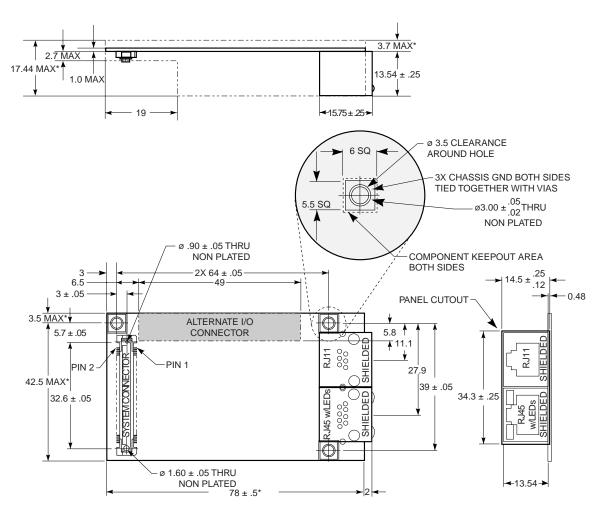

| Figure 5-7: Type IIIA Form Factor                                                    | 45 |

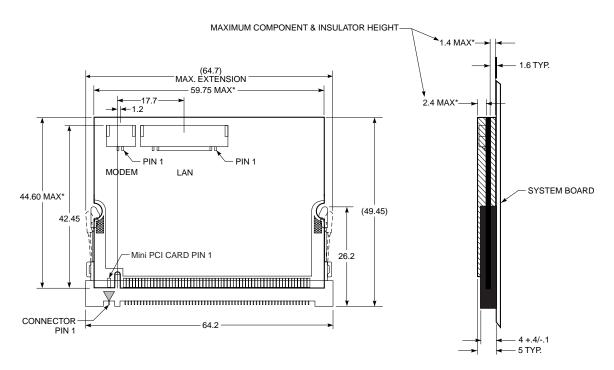

| Figure 5-8: Type IIIB Form Factor                                                    | 46 |

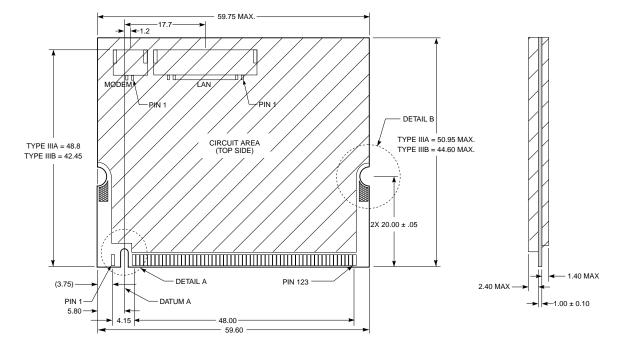

| Figure 5-9: Type III PCB Form Factor                                                 | 47 |

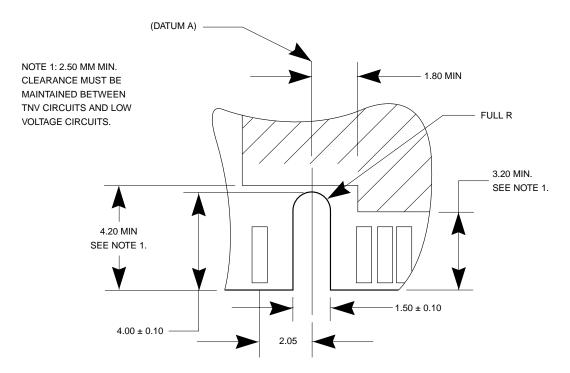

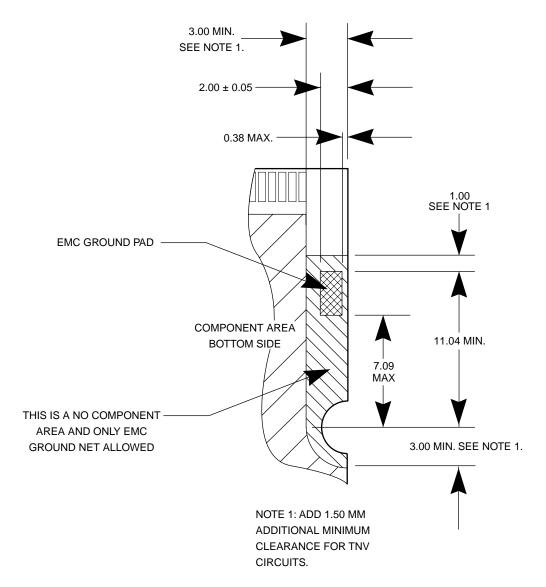

| Figure 5-10: Type III PCB, Top Side, Detail A                                        | 48 |

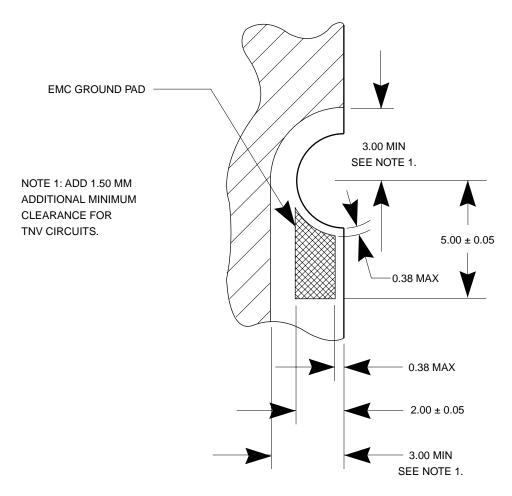

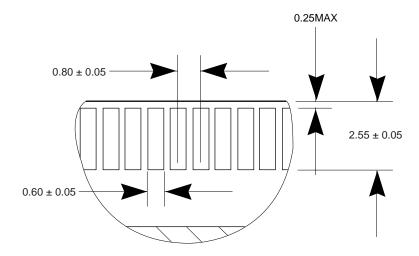

| Figure 5-11: Type III PCB, Top Side, Detail B (2X)                                   | 49 |

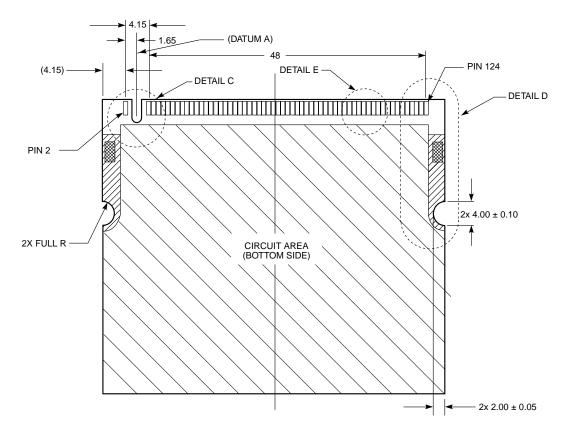

| Figure 5-12: Type III PCB, Bottom Side                                               |    |

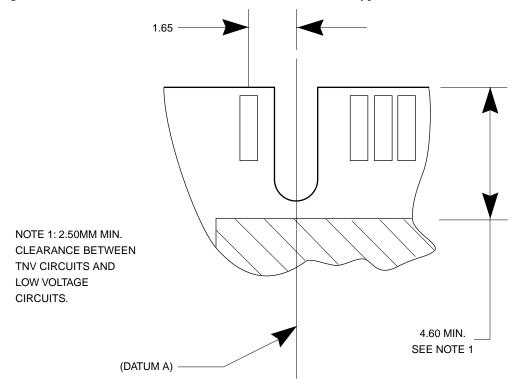

| Figure 5-13: Type III PCB, Bottom Side, Detail C                                     | 51 |

| Figure 5-14: Type III PCB, Bottom Side, Detail D (2X)                                | 52 |

| Figure 5-15: Type III PCB, Bottom Side, Detail E                                     | 53 |

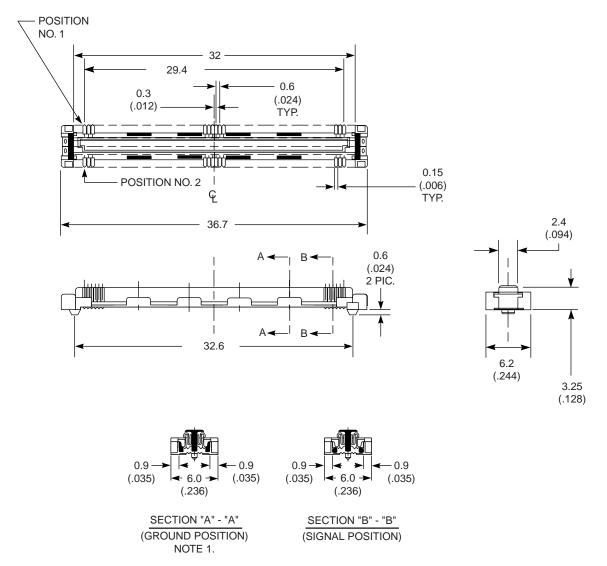

| Figure 5-16: Type I and Type II System Connector                                     | 55 |

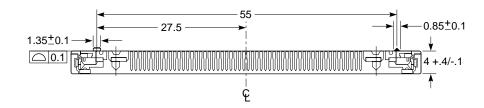

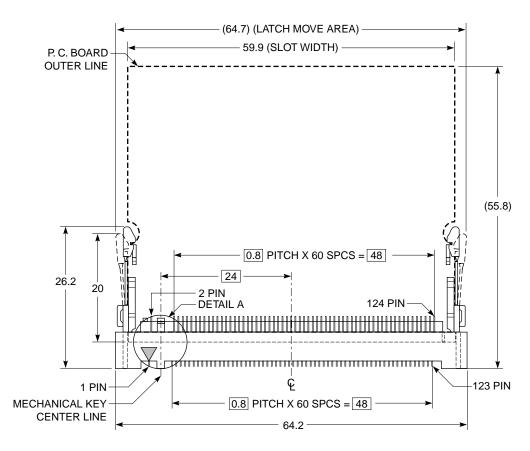

| Figure 5-17: Type III System Connector (Shown with Type IIIA Card Inserted)          | 57 |

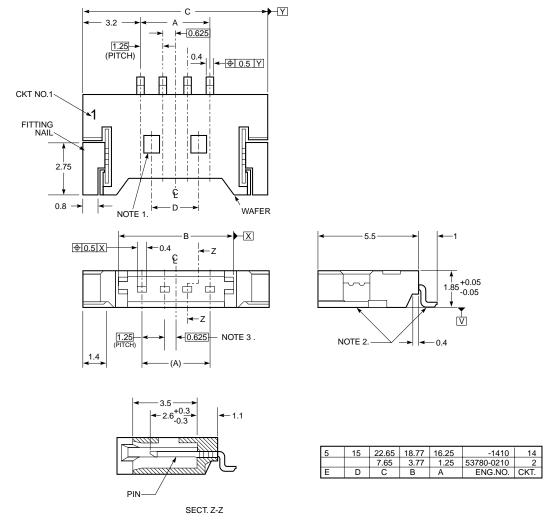

| Figure 5-18: Type I and Type III I/O Connectors                                      | 59 |

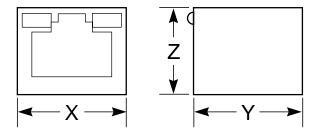

| Figure 5-19: RJ Connector Detail                                                     | 61 |

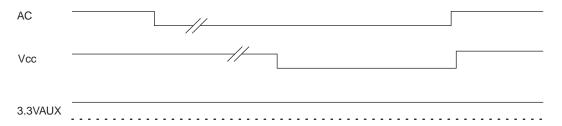

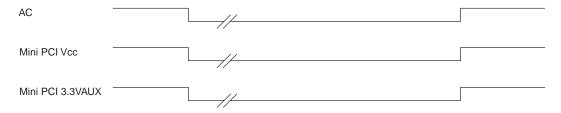

| Figure 7-1: 3.3VAUX Always Supported                                                 | 69 |

| Figure 7-2: D3 <sub>cold</sub> Support Only When On AC                               | 70 |

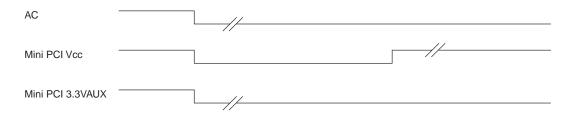

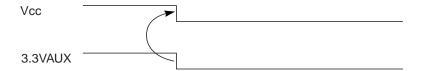

| Figure 7-3: Re-establishment of Mini PCI Card Without 3.3VAUX Support                | 70 |

| Figure 7-4: Loss of 3.3VAUX When 3.3V is Present                                     |    |

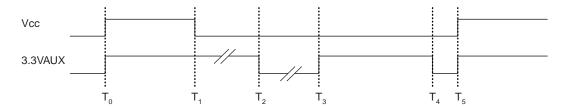

| Figure 7-5: Undefined 3.3VAUX Transitions                                            | 72 |

## **Tables**

| Table 2-1: Mini PCI Sideband Signals                                 | 9  |

|----------------------------------------------------------------------|----|

| Table 2-2: Mini PCI Card Type I/II System Connector Pinout           | 13 |

| Table 2-3: Mini PCI Card Type III System Connector Pinout            | 14 |

| Table 2-4: Type I and Type III LAN Connector Pinout                  | 15 |

| Table 2-5: Type I and Type III Modem Connector Pinout                | 16 |

| Table 3-1: System Connector Specifications                           | 18 |

| Table 3-2: Function-Specific Connector Specifications                | 19 |

| Table 4-1: System Connector Specifications                           | 21 |

| Table 4-2: Function-Specific Connector Specifications                | 25 |

| Table 5-1: Function-Specific Connector Specifications                | 31 |

| Table 5-2: 100-Pin Connector Physical Requirements                   | 56 |

| Table 5-3: 100-Pin Connector Mechanical Performance Specification    | 5e |

| Table 5-4: 100-Pin Connector Electrical Performance Specification    | 56 |

| Table 5-5: 100-Pin Connector Environmental Performance Specification | 5e |

| Table 5-6: 124-Pin Connector Physical Requirements                   |    |

| Table 5-7: 124-Pin Connector Mechanical Performance Specification    | 58 |

| Table 5-8: 124-Pin Connector Electrical Performance Specification    | 58 |

| Table 5-9: 124-Pin Connector Environmental Performance Specification | 58 |

| Table 5-10: I/O Connector Physical Requirements                      | 60 |

| Table 5-11: I/O Connector Mechanical Performance Specification       | 60 |

| Table 5-12: I/O Connector Electrical Performance Specification       | 60 |

| Table 5-13: I/O Connector Environmental Performance Specification    | 60 |

| Table 5-14: Representative Connector Information                     | 61 |

| Table 7-1: Mini PCI Power Management Exceptions                      | 65 |

| Table 7-2: Command Register Enable Bit                               | 73 |

# Chapter 1 Introduction

### 1.1 Overview

The Mini PCI Specification defines an alternate implementation for small form factor PCI cards referred to in this specification as a Mini PCI Card. This specification uses a qualified sub-set of the same signal protocol, electrical definitions, and configuration definitions as the *PCI Local Bus Specification*.

Where this specification does not explicitly define PCI characteristics, the *PCI Local Bus Specification* governs.

The primary differences between a standard PCI expansion card and a Mini PCI Card are:

- The form factor of the card and card-system interconnection, that is, the smaller physical size of the Mini PCI Card and the connectors it uses

- The use of standard sideband signals for audio and communications

- Support of the **CLKRUN#** signal defined in the *PCI Mobile Design Guide*

- No support for optional JTAG signals, nor for the 64-bit PCI extension defined in the PCI Local Bus Specification

### 1.2 Motivation

The performance characteristics of the PCI local bus, demonstrated in desktop and server systems, make PCI cards desirable in a wide range of systems. Proprietary form factor PCI cards are already commonplace, underscoring the need for a standard to simplify designs, reduce costs, and increase the number of implementation options.

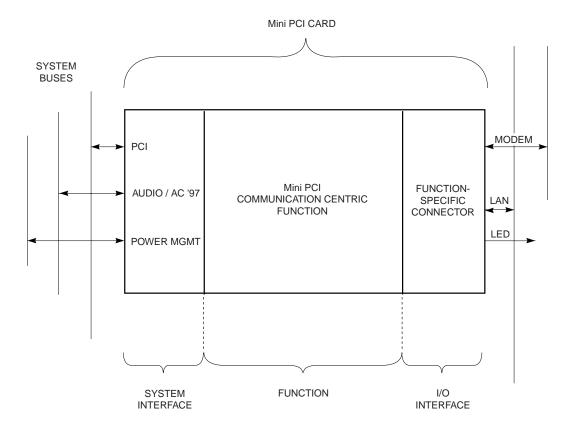

This specification defines a standard small-form-factor card (using the 32-bit PCI local bus) that can be used in smaller systems in which standard PCI and Small PCI expansion cards cannot be used due to mechanical system design constraints. Examples of such smaller systems include notebook PCs and docking stations, sealed-case PCs (Net PCs or NCs), and set top boxes integrating communications capabilities. Figure 1-1 is a logical representation of the Mini PCI Specification.

Figure 1-1: Logical Representation of the Mini PCI Specification

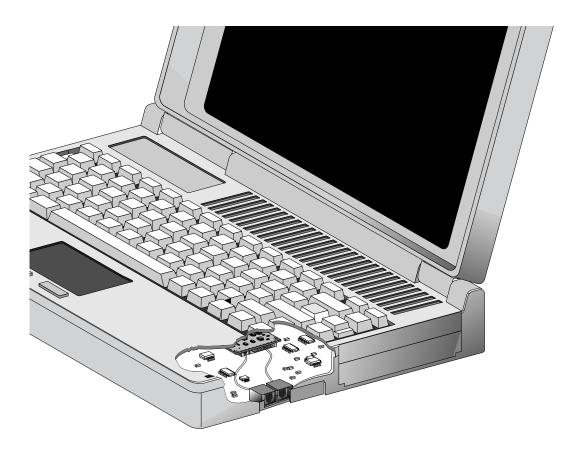

Figure 1-2 shows a cutaway view of a notebook computer with a Mini PCI Card installed. The illustration shows a conceptual placement of the card. Actual installation location depends on the manufacturer.

Figure 1-2: Type I/Type III Mini PCI Card in a Notebook Computer

### 1.3 Features and Benefits

This specification establishes a high-performance local-bus standard for small or restricted mechanical environments. The key features and benefits can be divided into two groups.

The first group of benefits comes from the use of an alternate form factor:

- **Upgradeability.** Mini PCI Cards are removable and upgradeable with available "new technology" cards. This allows upgrades to the newest technologies. Where required, it is the system manufacturer's responsibility to provide sufficient notification in the accompanying manual that service should be performed by a qualified technician.

- **Flexibility.** A single Mini PCI interface can accommodate various types of communications devices. Therefore, the OEM manufacturer can supply "build to order" systems (for example, a network interface card instead of a modem or Token Ring instead of Ethernet).

- **Reduced Cost.** A standard form factor for small form factor cards makes them more manufacturable, which reduces costs and provides economies-of-scale advantage over custom manufactured form factors.

- **Serviceability.** Mini PCI Cards can be removed and easily serviced if they fail.

- **Reliability.** Mini PCI Cards will be mass produced and, consequently, of higher quality than low-volume custom boards.

- Software Compatibility. Mini PCI Cards are intended to be fully compatible with existing software drivers and applications developed for standard PCI expansion cards. In addition, it is strongly recommended that all Mini PCI Cards support current industry standards such as the applicable version of the *PC XX System Design Guide* (currently at version PC 99), *Advanced Configuration and Power Interface Specification* (ACPI), and other industry initiatives that may be developed in the future.

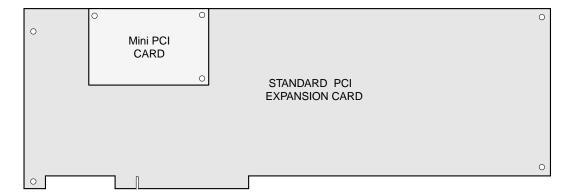

- **Reduced Size.** Mini PCI Cards are smaller than PCMCIA cards, Small PCI cards, and typical daughter boards. This reduced size permits a higher level of integration of data communications devices into notebook PCs, docking stations, sealed-case PCs (NetPCs or NCs), and set top boxes. Figure 1-3 shows a size comparison between the Type I Mini PCI Card and a standard PCI expansion card.

- Regulatory Agency Accepted Form Factor. Standardization of the Mini PCI Card form factor will permit world wide regulatory agencies to approve Mini PCI communications devices independent of host systems. This significantly reduces cost and risk on the part of systems manufacturers.

Figure 1-3: Mini PCI and Standard PCI Size Comparison

The second group of benefits derives from the use of the high-performance PCI local bus:

- **High Performance.** The PCI high-performance characteristics include 32-bit data path, full concurrency with the processor and memory subsystem, and hidden (overlapped) central arbitration.

- **Ease of Use.** Mini PCI supports full auto-configuration of PCI local bus add-in boards and components.

- Longevity. Implementing subsystems on the Mini PCI Cards increases system board utility. PCI local buses are processor independent and support multiple families of processors and future generations of processors (by bridges or by direct integration).

- **Flexibility.** PCI's full multi-master capability allows any PCI master peer-to-peer access to any PCI master/target.

- **Data Integrity.** PCI provides parity on both data and address and allows implementation of robust client platforms.

- **Power Management.** Consideration for mobile systems power requirements, PCI bus power management, and clock run protocol support.

### 1.4 Specification References

This specification should be used in conjunction with the following specifications and documents (which were at the corresponding version numbers at the time of writing):

- PCI Local Bus Specification, Revision 2.2

- PCI Bus Power Management Interface Specification, Revision 1.1

- PCI Mobile Design Guide, Version 1.1

- Audio Codec '97 Component Specification, Revision 2.1

- PC Card Standard Electrical Specification, Revision April 1998

- ISO/IEC 8802-3 ANSI IEEE Standard 802.3

- Supplement to ANSI/IEEE 802.3 Document 802.3u

- ISO/IEC 8802-5 ANSI IEEE Standard 802.5

Design considerations should adhere to the guidelines established in the applicable revision of the *PC XX System Design Guide* (currently at version PC 99).

### 1.5 Administration

This document is maintained by the PCI SIG. The PCI SIG, an unincorporated association of members of the microcomputer industry, was established to monitor and enhance the development of the PCI local bus.

SIG membership is available to all applicants within the microcomputer industry. Benefits of membership include:

- Ability to submit specification revisions and addendum proposals

- Participation in specification revisions and addendum proposals

- Automatically receive revisions and addenda

- Voting rights to determine the Steering Committee membership

- Vendor ID number assignment

- PCI technical support

- PCI support documentation and materials

- Participation in SIG sponsored trade show suites and events, conferences, and other PCI local bus promotional activities

- Participation in the compliance program including participation at the "PCI Compliance Workshops" and the opportunity to be included in the "PCI Integrator's List"

For information on how to become a SIG member or on obtaining PCI local bus documentation, please contact:

PCI Special Interest Group 2575 N.E. Kathryn #17 Hillsboro, Oregon 97124

Phone: 800-433-5177 (Inside the U.S.)

503-693-6360 (Outside the U.S.)

Fax: 503-693-8344 e-mail: pcisig@pcisig.com Internet: http://www.pcisig.com

# Chapter 2 Signal Definition

### 2.1 PCI Local Bus Specification References

The Mini PCI Card system interface implements the following:

- A qualified sub-set of the signals required by a PCI interface. Bridging is supported but must be implemented without the **LOCK#** signal.

- Some optional PCI signals.

- A number of additional sideband signals.

Because the Mini PCI Card system interface is implemented with a supply voltage (Vcc) of 3.3 volts, and the bus interface signals are 3.3 volts, there is no requirement that the Mini PCI Card implement a 5 volt tolerant bus interface architecture. The Mini PCI signal set can be divided into three sub-sets:

- PCI interface

- PCI power management

- Sideband

Sideband signals provide audio and communications support.

### 2.2 System Connector Interface Signals

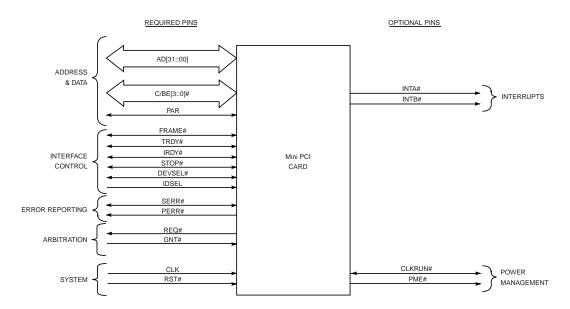

The Mini PCI Card PCI interface signal sub-set is defined in Figure 2-1.

Figure 2-1: Mini PCI Card System PCI Signal Set

The signals follow the specifications as defined in Chapter 2 of the *PCI Local Bus Specification*. All signal directions are specified with respect to the system board.

Mini PCI power management consists of the following:

- PCI power bus management signals PME# and 3.3VAUX as defined in the PCI Bus Power Management Interface Specification, with the exceptions noted in Chapter 7 of this document

- **CLKRUN#** as defined in the *PCI Mobile Design Guide*

This specification does not require that the system board implement Mobile PCI's clock run. If clock run is not implemented on the system board, the clock run pin on the system connector must be terminated low on the system board. This specification does require that the Mini PCI Card implement clock run functionality. Functionality does not allow for terminating the **CLKRUN#** pin to ground or through a pull-down resistor to indicate that the Mini PCI Card cannot tolerate a stopped or slowed clock. If the Mini PCI Card cannot tolerate the clock stopping or slowing, the Mini PCI Card must implement the clock run protocol and indicate that the clock cannot be stopped according to the *Mobile PCI Design Guide*. Only if the Mini PCI Card can tolerate the clock being stopped or slowed at any time without notification and the Mini PCI Card will never need to restart the clock, can the Mini PCI Card implement clock run as a no connect.

Clock run cannot be implemented with a static pull-down or repetitive pulse circuit. The protocol must be supported or the implementation must be insensitive to clock stopping or slowing down.

Telephony audio support is provided by the SYS\_AUDIO\_IN, SYS\_AUDIO\_OUT, and the MOD\_AUDIO\_MON pins. Future modem support is available using the *Audio Codec '97 Component Specification* interface.

These signals are shown in Table 2-1. All signal directions are specified with respect to the system board.

Table 2-1: Mini PCI Sideband Signals

| Signal Group                   | Signal      | Direction    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------|-------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power<br>Management<br>Support | 3.3VAUX     | Output       | Auxiliary 3.3Vcc support for PME#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                | CLKRUN#     | Input/Output | Control signal for PCI CLK. Used to stop or start the PCI clock for power management purposes. Also used to indicate the requirement for re-starting the clock or indicating that the PCI function cannot tolerate stopping the PCI clock.                                                                                                                                                                                                                                                                                                                                                                           |

|                                | PME#        | Input        | Control signal indicating a power management event has occurred.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                | MPCIACT#    | Input        | Mini PCI function active. Intended to indicate, when low, that the Mini PCI Card is in a communicating state requiring full system performance; for example, a software modem in the off hook state.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AC-link                        | AC_SYNC     | Output       | Audio Codec '97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Support                        |             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Support                        | AC_SDATA_IN | Input        | Audio Codec '97  This corresponds to the SDATA_INx pin of the AC-link specification where "x" is 0, 1, 2, or 3. It is the responsibility of the system designer to properly connect the AC_SDATA_IN pin to the correct SDATA_IN pin of the system. If the system requires that the codec on the Mini PCI Card be a primary codec, then the system must hook the AC_SDATA_IN pin to SDATA_INO on the system board. If the system requires that the codec on the Mini PCI Card be a secondary codec, the system must hook the AC_SDATA_IN pin to the proper SDATA_INy pin on the system board where "y" is 1, 2, or 3. |

Table 2-1. Mini PCI Sideband Signals (continued)

| Signal Group           | Signal                                            | Direction    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|------------------------|---------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                        | AC_BIT_CLK                                        | Input/Output | Audio Codec '97                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| AC-link                | AC_CODEC_ID0#,                                    | Output       | Audio Codec '97                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Support                | AC_CODEC_ID1#                                     |              | Used to assign the Mini PCI AC, AMC, or MC codec to the correct primary or secondary codec address. The system board manufacturer sets these bits based on the connection of AC_SDATA_IN to its respective SDATA_INx pin. A logic high voltage should be tied to the Wake voltage of the Mini PCI Card (3.3VAUX or 3.3V if 3.3VAUX is not used)  Connection ID1 ID0 SDATA_IN0 0 0 SDATA_IN1 0 1 SDATA_IN2 1 0 SDATA_IN2 1 0 SDATA_IN3 1 1 Note that the pins are |  |  |  |

|                        | AC_SDATA_OUT                                      | Output       | logically TRUE when low.  Audio Codec '97                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                        | AC_RESET#                                         | Output       | Audio Codec '97                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Audio Support          | AUDIO_GND                                         | Output       | Analog ground for line level audio                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                        | MOD_AUDIO_MON                                     | Input        | Modem audio monitor                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                        | SYS_AUDIO_IN                                      | Input        | Telephony audio support                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                        | SYS_AUDIO_OUT                                     | Output       | Telephony audio support                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                        | SYS_AUDIO_IN_GND <sup>1</sup>                     | Input        | Return for SYS_AUDIO_IN                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                        | SYS_AUDIO_OUT_GND <sup>1</sup>                    | Output       | Return for SYS_AUDIO_OUT                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Phoneline<br>Interface | TIP <sup>1</sup>                                  | Input/Output | Analog phoneline interface for modems                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                        | RING <sup>1</sup>                                 | Input/Output | Analog phoneline interface for modems                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| LAN Interface          | See Table 2-4 for signal assignments <sup>1</sup> | Input/Output | LAN and LAN LED connections                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Analog Power           | VCC5VA <sup>1</sup>                               | Output       | 5 volt power for analog voice circuits                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

A number of pins are defined as "RESERVED." These pins are reserved for future expansion and must not be connected on the Mini PCI Card or the host platform.

$<sup>^{\</sup>mbox{\scriptsize 1}}$  Available on the system connector in the Type III form factor only.

The signals denoted Audio Codec '97 constitute audio support as defined in the *Audio Codec* '97 *Component Specification*. The host platform support of AC link signals is optional. If AC link signals are supported, the host platform may need to terminate, with weak pulldowns or pullups as required by the system board chipset, the AC\_BIT\_CLK and AC\_SDATA\_IN signals to cover instances where the Mini PCI Card is not present or where it does not support AC link. Host platforms not supporting AC-link shall terminate the following signals to ground with less than or equal to 10 kohm termination: AC\_RESET#, AC\_BIT\_CLK, AC\_SYNC, and AC\_SDATA\_OUT. Host platforms not supporting AC-link shall terminate the following signals to Wake voltage with less than or equal to 100 kohm termination: AC\_CODEC\_ID0# and AC\_CODEC\_ID1#.

Interrupt support is indicated by PCI interrupts **INTA#** and **INTB#**. PCI 66 MHz bus clock support is provided by **M66EN**. The PCI interrupts and **M66EN** are defined in Chapter 2 of the *PCI Local Bus Specification*.

As a system board device, Mini PCI interrupt support implements some of the latitude afforded system board devices in interrupt assignments as defined in the *PCI Local Bus Specification*, Section 2.2.6.

### 2.2.1 Modem and System Audio Support

The MOD\_AUDIO\_MON signal supports Pulse Width Modulation (PWM) modem call progress monitoring. Implementation of the MOD\_AUDIO\_MON (Modem Audio Monitor) is defined in the *PCMCIA PC Card Standard–Electrical Specification*, Section 5.2.12. The MOD\_AUDIO\_MON signal is required for data/fax (non-voice) only modem implementations. However, this signal is optional for the purposes of call progress monitoring in voice/data/fax modem implementations.

The definitions for SYS\_AUDIO\_IN (system audio input from the Mini PCI Card) and SYS\_AUDIO\_OUT (system audio output to the Mini PCI Card) are line-level audio signals intended to support modem speakerphone type implementations. These signals are required for voice/data/fax modem implementations. These signals are optional for data/fax only modem implementations. Examples are shown in Figures 4-1 and 4-2. The electrical parameters of SYS\_AUDIO\_IN and SYS\_AUDIO\_OUT can be found in Chapter 4 of this document.

The Type III Mini PCI form factor has two additional signals, SYS\_AUDIO\_IN\_GND and SYS\_AUDIO\_OUT\_GND, which may be used to support different audio implementations. Chapter 4 describes these different implementations.

### 2.3 Mini PCI Exceptions and Differences

Mini PCI differs from the *PCI Local Bus Specification* in the following ways:

- While the *PCI Local Bus Specification* defines 5V, 3.3V, and dual voltage add-in cards, Mini PCI supports only a 3.3V signaling environment. Therefore, there are no V<sub>I/O</sub> pins defined, and no connector keying. The main Vcc logic supply is 3.3V. 5V is available, but limited to 100 mA.

- Total power consumption from all sources is limited to 2.0 W.

- The 5V supply defined for Type I, II, and III Mini PCI Cards is limited to 100 mA.

The VCC5VA defined for Type III only Mini PCI Cards (filtered audio 5V supply) is limited to 100 mA. The 5V and VCC5VA supply are not the same supply and cannot be connected on the Mini PCI Card. See Table 4-1 for more information regarding VCC5VA.

- 3.3VAUX is limited to 200 mA in D3 states with PME enabled and to less than 5 mA in D3 states when PME is not enabled. In D0, D1, and D2 states, it is acceptable for wake event capable Mini PCI applications to consume up to 375 mA of 3.3VAUX current.

- PCI 64-bit bus expansion is not supported.

- Maximum connector pin current capacity is 500 mA.

- +12V and -12V supplies are not implemented.

- Uninitialized (D0 uninitialized) current is limited to 70 mA rather than the 10 W afforded a standard PCI expansion card.

- Caching is not supported.

- Since a Mini PCI Card is discovered through normal IDSEL and configuration read sequences, the PRESENT pins are not required or supported. Some interrupt routing latitude, typically reserved for the system board, is allocated to the Mini PCI Card

- Power management is required.

- The **LOCK#** signal is not supported.

- Mini PCI is 3.3V signaling only.

### 2.4 System Connector Pinout

The pin list in Table 2-2 shows system connector pinout for Type I and Type II cards. The pin list in Table 2-3 shows the system connector pinout for Type III cards.

Table 2-2: Mini PCI Card Type I/II System Connector Pinout

| Pin | Signal   | Pin | Signal   | Pin | Signal        | Pin | Signal                    |

|-----|----------|-----|----------|-----|---------------|-----|---------------------------|

| 1   | INTB#    | 2   | 5V       | 51  | SERR#         | 52  | STOP#                     |

| 3   | 3.3V     | 4   | INTA#    | 53  | GROUND        | 54  | 3.3V                      |

| 5   | RESERVED | 6   | RESERVED | 55  | PERR#         | 56  | DEVSEL#                   |

| 7   | GROUND   | 8   | 3.3VAUX  | 57  | C/BE[1]#      | 58  | GROUND                    |

| 9   | CLK      | 10  | RST#     | 59  | AD[14]        | 60  | AD[15]                    |

| 11  | GROUND   | 12  | 3.3V     | 61  | GROUND        | 62  | AD[13]                    |

| 13  | REQ#     | 14  | GNT#     | 63  | AD[12]        | 64  | AD[11]                    |

| 15  | 3.3V     | 16  | GROUND   | 65  | AD[10]        | 66  | GROUND                    |

| 17  | AD[31]   | 18  | PME#     | 67  | GROUND        | 68  | AD[09]                    |

| 19  | AD[29]   | 20  | RESERVED | 69  | AD[08]        | 70  | C/BE[0]#                  |

| 21  | GROUND   | 22  | AD[30]   | 71  | AD[07]        | 72  | 3.3V                      |

| 23  | AD[27]   | 24  | 3.3V     | 73  | 3.3V          | 74  | AD[06]                    |

| 25  | AD[25]   | 26  | AD[28]   | 75  | AD[05]        | 76  | AD[04]                    |

| 27  | RESERVED | 28  | AD[26]   | 77  | RESERVED      | 78  | AD[02]                    |

| 29  | C/BE[3]# | 30  | AD[24]   | 79  | AD[03]        | 80  | AD[00]                    |

| 31  | AD[23]   | 32  | IDSEL    | 81  | 5V            | 82  | RESERVED_WIP <sup>2</sup> |

| 33  | GROUND   | 34  | GROUND   | 83  | AD[01]        | 84  | RESERVED_WIP <sup>2</sup> |

| 35  | AD[21]   | 36  | AD[22]   | 85  | GROUND        | 86  | GROUND                    |

| 37  | AD[19]   | 38  | AD[20]   | 87  | AC_SYNC       | 88  | M66EN                     |

| 39  | GROUND   | 40  | PAR      | 89  | AC_SDATA_IN   | 90  | AC_SDATA_OUT              |

| 41  | AD[17]   | 42  | AD[18]   | 91  | AC_BIT_CLK    | 92  | AC_CODEC_ID0#             |

| 43  | C/BE[2]# | 44  | AD[16]   | 93  | AC_CODEC_ID1# | 94  | AC_RESET#                 |

| 45  | IRDY#    | 46  | GROUND   | 95  | MOD_AUDIO_MON | 96  | RESERVED                  |

| 47  | 3.3V     | 48  | FRAME#   | 97  | AUDIO_GND     | 98  | GROUND                    |

| 49  | CLKRUN#  | 50  | TRDY#    | 99  | SYS_AUDIO_OUT | 100 | SYS_AUDIO_IN              |

<sup>&</sup>lt;sup>2</sup> Work in progress by the Mini PCI Working Group System Connector Sub Group.

Note that the Type III system connector is a superset of the Type I and II connectors. The signal list and layout in Table 2-3 starting at pin 17 is equivalent to pin 1 in Table 2-2. The overlapping signal region is shaded in Table 2-3.

Table 2-3: Mini PCI Card Type III System Connector Pinout

| Pin | Signal                 | Pin | Signal                 | Pin | Pin Signal        |     | in Signal                 |  |

|-----|------------------------|-----|------------------------|-----|-------------------|-----|---------------------------|--|

| 1   | TIP                    | 2   | RING                   | 63  | 3.3V              | 64  | FRAME#                    |  |

|     | Key                    |     | Key                    | 65  | CLKRUN#           | 66  | TRDY#                     |  |

| 3   | 8PMJ-3 <sup>3, 4</sup> | 4   | 8PMJ-1 <sup>3, 4</sup> | 67  | SERR#             | 68  | STOP#                     |  |

| 5   | 8PMJ-6 <sup>3, 4</sup> | 6   | 8PMJ-2 <sup>3, 4</sup> | 69  | GROUND            | 70  | 3.3V                      |  |

| 7   | 8PMJ-7 <sup>3, 4</sup> | 8   | 8PMJ-4 <sup>3, 4</sup> | 71  | PERR#             | 72  | DEVSEL#                   |  |

| 9   | 8PMJ-8 <sup>3, 4</sup> | 10  | 8PMJ-5 <sup>3, 4</sup> | 73  | C/BE[1]#          | 74  | GROUND                    |  |

| 11  | LED1_GRNP              | 12  | LED2_YELP              | 75  | AD[14]            | 76  | AD[15]                    |  |

| 13  | LED1_GRNN              | 14  | LED2_YELN              | 77  | GROUND            | 78  | AD[13]                    |  |

| 15  | CHSGND                 | 16  | RESERVED               | 79  | AD[12]            | 80  | AD[11]                    |  |

| 17  | INTB#                  | 18  | 5V                     | 81  | AD[10]            | 82  | GROUND                    |  |

| 19  | 3.3V                   | 20  | INTA#                  | 83  | GROUND            | 84  | AD[09]                    |  |

| 21  | RESERVED               | 22  | RESERVED               | 85  | AD[08]            | 86  | C/BE[0]#                  |  |

| 23  | GROUND                 | 24  | 3.3VAUX                | 87  | AD[07]            | 88  | 3.3V                      |  |

| 25  | CLK                    | 26  | RST#                   | 89  | 3.3V              | 90  | AD[06]                    |  |

| 27  | GROUND                 | 28  | 3.3V                   | 91  | AD[05]            | 92  | AD[04]                    |  |

| 29  | REQ#                   | 30  | GNT#                   | 93  | RESERVED          | 94  | AD[02]                    |  |

| 31  | 3.3V                   | 32  | GROUND                 | 95  | AD[03]            | 96  | AD[00]                    |  |

| 33  | AD[31]                 | 34  | PME#                   | 97  | 5V                | 98  | RESERVED_WIP <sup>5</sup> |  |

| 35  | AD[29]                 | 36  | RESERVED               | 99  | AD[01]            | 100 | RESERVED_WIP <sup>5</sup> |  |

| 37  | GROUND                 | 38  | AD[30]                 | 101 | GROUND            | 102 | GROUND                    |  |

| 39  | AD[27]                 | 40  | 3.3V                   | 103 | AC_SYNC           | 104 | M66EN                     |  |

| 41  | AD[25]                 | 42  | AD[28]                 | 105 | AC_SDATA_IN       | 106 | AC_SDATA_OUT              |  |

| 43  | RESERVED               | 44  | AD[26]                 | 107 | AC_BIT_CLK        | 108 | AC_CODEC_ID0#             |  |

| 45  | C/BE[3]#               | 46  | AD[24]                 | 109 | AC_CODEC_ID1#     | 110 | AC_RESET#                 |  |

| 47  | AD[23]                 | 48  | IDSEL                  | 111 | MOD_AUDIO_MON     | 112 | RESERVED                  |  |

| 49  | GROUND                 | 50  | GROUND                 | 113 | AUDIO_GND         | 114 | GROUND                    |  |

| 51  | AD[21]                 | 52  | AD[22]                 | 115 | SYS_AUDIO_OUT     | 116 | SYS_AUDIO_IN              |  |

| 53  | AD[19]                 | 54  | AD[20]                 | 117 | SYS_AUDIO_OUT GND | 118 | SYS_AUDIO_IN GND          |  |

| 55  | GROUND                 | 56  | PAR                    | 119 | AUDIO_GND         | 120 | AUDIO_GND                 |  |

| 57  | AD[17]                 | 58  | AD[18]                 | 121 | RESERVED          | 122 | MPCIACT#                  |  |

| 59  | C/BE[2]#               | 60  | AD[16]                 | 123 | VCC5VA            | 124 | 3.3VAUX                   |  |

| 61  | IRDY#                  | 62  | GROUND                 |     | •                 |     | •                         |  |

<sup>&</sup>lt;sup>3</sup> 8PMJ = 8 position modular jack connector pin, hereinafter referred to as RJ45 (see IEC 603-7:1990), see Table 2-4 for details.

<sup>&</sup>lt;sup>4</sup> Note: These signals are optional and are defined to provide convenient access to LAN signals without cabling. However, due to voltage limitations of the Type III connector, additional insulation or engineering will be required to meet IEEE 802.3 and 802.5 electrical isolation requirements.

$<sup>^{5}</sup>$  Work in progress by the Mini PCI Working Group System Connector Sub Group.

### 2.5 Function-Specific Connectors-Communications Support

This section describes the 8 position modular jack LAN connector, hereinafter referred to as RJ45 (see IEC 603-7:1990), support for the Mini PCI Type I and Type III Cards only because Type II Cards have built in RJ connectors. Those RJ connector pinouts must be in compliance with the following specifications:

- ISO/IEC 8802-3 ANSI IEEE Standard 802.3

- Supplement to ANSI/IEEE 802.3 Document 802.3u

- ISO/IEC 8802-5 ANSI IEEE Standard 802.5

Table 2-4 shows Type I and Type III LAN connector pinout.

Table 2-4: Type I and Type III LAN Connector Pinout

| I/O<br>Conn      |                         | RJ45<br>(8PMJ)          | Type III<br>System<br>Connector |     |                  |

|------------------|-------------------------|-------------------------|---------------------------------|-----|------------------|

| Pin <sup>6</sup> | 10 BASE-T               | 10-100                  | Token Ring                      | Pin | Pin <sup>6</sup> |

| 1                | LED1_GRNP <sup>7</sup>  | LED1_GRNP <sup>7</sup>  | LED1_GRNP <sup>7</sup>          |     | 11               |

| 2                | LED1_GRNN <sup>7</sup>  | LED1_GRNN <sup>7</sup>  | LED1_GRNN <sup>7</sup>          |     | 13               |

| 3                | No Connect <sup>8</sup> | No Connect <sup>8</sup> | No Connect <sup>8</sup>         |     | 15               |

| 4                | Not used                | RJ45 termination        | Optionally terminated           | 8   | 9                |

| 5                | Not used                | RJ45 termination        | Optionally terminated           | 7   | 7                |

| 6                | RD-                     | RD-                     | TX+                             | 6   | 5                |

| 7                | Not used                | RJ45 termination        | RX-                             | 5   | 10               |

| 8                | Not used                | RJ45 termination        | RX+                             | 4   | 8                |

| 9                | RD+                     | RD+                     | TX-                             | 3   | 3                |

| 10               | TD-                     | TD-                     | Optionally terminated           | 2   | 6                |

| 11               | TD+                     | TD+                     | Optionally terminated           | 1   | 4                |

| 12               | No Connect <sup>8</sup> | No Connect <sup>8</sup> | No Connect <sup>8</sup>         |     |                  |

| 13               | LED2_YELP <sup>7</sup>  | LED2_YELP <sup>7</sup>  | LED2_YELP <sup>7</sup>          |     | 12               |

| 14               | LED2_YELN <sup>7</sup>  | LED2_YELN <sup>7</sup>  | LED2_YELN <sup>7</sup>          |     | 14               |

<sup>&</sup>lt;sup>6</sup> Due to the high frequencies on the LAN signals, Type III implementations shall not use both an I/O connector and a system connector for LAN wiring. The Type III card and host systems supporting Type III cards must be configured for only one connector, either an I/O connector or a system connector, but not both. Using both connectors will have an adverse affect on LAN performance and reliability. Host systems shall designate which form of connection is available on the host system and only incorporate Mini PCI Cards with matching configurations. Note: The Type III system connector wiring for LAN signals is defined to provide convenient access to LAN signals without cabling. However, due to voltage limitations of the Type III connector, additional insulation or engineering will be required to meet IEEE 802.3 and 802.5 electrical isolation requirements.

<sup>&</sup>lt;sup>7</sup> LED signals are optional and, if connected, are only required on the connector used for LAN signals. LED signals do not need to be wired to both the I/O Connector and the System Connector on Type III cards.

<sup>&</sup>lt;sup>8</sup> This pin must be left as No Connect in order to meet IEEE 802.3 and 802.5 electrical isolation requirements.

Table 2-5 shows the pinout for the Type I and Type III modem connector.

Table 2-5: Type I and Type III Modem Connector Pinout

| Pin # | Signal | Description                                                                                                       |

|-------|--------|-------------------------------------------------------------------------------------------------------------------|

| 1     | RING   | RING is one conductor of the wire pair comprising the local loop.                                                 |

| 2     | TIP    | TIP is one conductor of the wire pair comprising the local loop. Usually the more positive of the two conductors. |

Type II modem Cards will have built-in RJ connectors whose pinouts must be in compliance with each country's regulatory agency specifications as discussed in Section 4.3.

### 2.5.1 LED Support

In addition to the standard LAN signal support, the Mini PCI implementation can support two LED devices in support of LAN functionality only. These LED devices can also be used in supporting LAN diagnostics which may be implementation specific. The Mini PCI Card generates and drives or sinks the LED device current as defined in Section 4.2.1. The LED device interface is supported as described in the LAN function-specific connector, as shown in Table 2-4; and optionally in the Type III system connector, as shown in Table 2-3. It is intended that one LED device be green. The second LED may be yellow, orange, or amber.

LED signals are optional and, if connected, are only required on the connector used for LAN signals. LED signals do not need to be wired to both the I/O Connector and the System Connector on Type III cards.

The LED devices are driven by the signals LEDx-yyyz where:

- x is the number 1 or 2 LED device.

- yyy indicates the color (YEL for yellow in this implementation).

- z indicates the DC polarity: N for sinking current into the pin, and P for sourcing current out of the pin.

As Table 2-4 shows, these signals then become LED1\_GRNN and LED1\_GRNP for the green LED device and LED2\_YELN and LED2\_YELP for the yellow LED device.

There is no standard convention for the implementation of LEDs for Token Ring or Ethernet. Therefore, LED functionality for the two LEDs for Token Ring and Ethernet is left undefined. Vendors are free to implement the two LEDs as they choose.

### 2.5.2 Chassis Ground

The signal CHSGND is a chassis ground contact and is connected on the Mini PCI Card through a mounting hole on Type I and Type II cards and via a spring contact clip on Type III cards (as illustrated in Chapter 5).

# Chapter 3 Buses

### 3.1 Introduction

In addition to the PCI bus, Mini PCI provides for implementing several technologies which may be enumerated as buses for discussion purposes as illustrated in Figure 1-1. The buses used in a Mini PCI Card implementation consist of combinations of the following:

- The PCI local bus

- An audio bus

- A power management bus

- LAN (Ethernet and Token Ring) buses

- A modem bus

Existing specifications define the implementations of these functional buses.

### 3.2 System Connector

Table 3-1 summarizes the appropriate specifications regarding the buses implemented in the Mini PCI Card system connector.

**Table 3-1: System Connector Specifications**

| Signals                                                                                                                                            | Bus Implementation | Governing Specification                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------|

| INTA#, INTB#, C/BE[0::3]#,<br>STOP#, DEVSEL#, IDSEL,<br>CLK, RST#, AD[00::31],<br>REQ#, GNT#, PAR, PERR#,<br>SERR#, M66EN, IRDY#,<br>TRDY#, FRAME# | PCI                | PCI Local Bus Specification,<br>Chapter 3                                                                      |

| PME#, 3.3VAUX                                                                                                                                      | Power management   | PCI Bus Power Management<br>Interface Specification                                                            |

| CLKRUN#                                                                                                                                            | Power management   | PCI Mobile Design Guide                                                                                        |

| AC_SYNC, AC_SDATA_IN,<br>AC_SDATA_OUT,<br>AC_BIT_CLK,<br>AC_CODEC_ID0#,<br>AC_CODEC_ID1#,<br>AC_RESET#                                             | AC-link support    | Audio Codec '97 Component<br>Specification                                                                     |

| MOD_AUDIO_MON,<br>SYS_AUDIO_OUT,<br>SYS_AUDIO_IN,<br>SYS_AUDIO_OUT_GND <sup>9</sup>                                                                | System audio       | These audio signals are implementation specific. Refer to Chapter 4 of this specification for characteristics. |

| SYS_AUDIO_IN_GND <sup>9</sup>                                                                                                                      |                    |                                                                                                                |

| AUDIO_GND                                                                                                                                          |                    |                                                                                                                |

| TIP <sup>9</sup> , RING <sup>9</sup>                                                                                                               | Modem              | Specific to country's regulatory agency specifications                                                         |

| 8PMJ1-8 <sup>9,10</sup>                                                                                                                            | LAN                | Refer to Table 3-2 for governing specifications                                                                |

$<sup>^{9}</sup>$  Available on the system connector in the Type III form factor only.

$<sup>^{10}</sup>$  Note: These signals are optional and are defined to provide convenient access to LAN signals without cabling. However, due to voltage limitations of the Type III connector, additional insulation or engineering will be required to meet IEEE 802.3 and 802.5 electrical isolation requirements.

### 3.3 Function-Specific Connector

Table 3-2 summarizes the appropriate specifications regarding the buses implemented in the Mini PCI Card function-specific connector.

**Table 3-2: Function-Specific Connector Specifications**

| Signals                                       | Bus Implementation         | Governing Specification                                                                        |

|-----------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------|

| RD-, RD+, TD-, TD+                            | Ethernet                   | ISO/IEC 8802-3 ANSI IEEE<br>Standard 802.3<br>Supplement to ANSI/IEEE<br>802.3 Document 802.3u |

| TX-, TX+, RX-, RX+                            | Token Ring                 | ISO/IEC 8802-5 ANSI IEEE<br>Standard 802.5                                                     |

| TIP, RING                                     | Modem                      | Specific to country's regulatory agency specifications                                         |

| LED1_GRNP, LED1_GRNN,<br>LED2_YELP, LED2_YELN | Local area network support | Implementation specific                                                                        |

| RJ45 termination                              | Local area network support | Technology specific                                                                            |

# Chapter 4 Electrical Specification

### 4.1 System Interface Connector

The electrical characteristics of each bus specified in this specification are implemented according to the relevant bus specification as shown in Table 4-1.

An exception exists for Mini PCI with regard to the implementation of the PCI bus **CLK** signal. The *PCI Local Bus Specification* requires that the **CLK** signal be 2.5 inches in length on the PCI card. This length is reduced to 25.4 mm ±2.5 mm (1.0 inch ±0.1 inches) for the Mini PCI Card and must be routed to only one load. This deviation from the *PCI Local Bus Specification* requires that the system board design be responsible for clock/data timing. All other characteristics of the **CLK** signal are as defined in the *PCI Local Bus Specification*.

**Table 4-1: System Connector Specifications**

| System Connector                                                                                                                                |                                      |                                                         |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------|--|

| Signals                                                                                                                                         | Bus Implementation                   | Governing Specification                                 |  |

| INTA#, INTB#, C/BE[0::3]#, STOP#,<br>DEVSEL#, IDSEL, CLK, RST#,<br>AD[00::31], REQ#, GNT#, PAR,<br>PERR#, SERR#, M66EN, IRDY#,<br>TRDY#, FRAME# | PCI                                  | PCI Local Bus<br>Specification, Chapter 4               |  |

| PME#, 3.3VAUX                                                                                                                                   | Power management                     | PCI Bus Power<br>Management Interface<br>Specificiation |  |

| CLKRUN#                                                                                                                                         | Power management                     | PCI Mobile Design Guide                                 |  |

| MPCIACT#                                                                                                                                        | Power management and general purpose | Refer to Section 4.5 for more information.              |  |

| AC_SYNC, AC_SDATA_IN, AC_SDATA_OUT, AC_BIT_CLK, AC_CODEC_ID0#, AC_CODEC_ID1#, AC_RESET#                                                         | AC-link support                      | Audio Codec '97<br>Component Specification              |  |

**Table 4-1: System Connector Specifications** (continued)

| System Connector                       |                                                                                                                                                                                                                                          |                                                                                     |                                                       |                                                 |                                                                                   |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------|

| Signals                                | Bus Implementation                                                                                                                                                                                                                       |                                                                                     | Governing<br>Specification                            |                                                 |                                                                                   |

| TIP <sup>11</sup> , RING <sup>11</sup> |                                                                                                                                                                                                                                          | Modem                                                                               |                                                       | regulator<br>specifica<br>Section               | to country's<br>ry agency<br>tions. Refer to<br>4.1.1 for specific<br>ound rules. |

| 8PMJ1-8 <sup>11</sup> , <sup>12</sup>  | LAN                                                                                                                                                                                                                                      |                                                                                     |                                                       | Refer to Table 4-2 for governing specifications |                                                                                   |

|                                        | ;                                                                                                                                                                                                                                        | System Audio                                                                        |                                                       |                                                 |                                                                                   |

| System Audio Signal                    | Volta                                                                                                                                                                                                                                    | ge Range                                                                            | Imped                                                 | ance                                            | Test Conditions                                                                   |

| SYS_AUDIO_OUT                          |                                                                                                                                                                                                                                          | 700 mV RMS Nominal 1000 mV RMS Max  Mini PCI terminatio impedance minimum System se |                                                       | n<br>e: 50 kΩ                                   | 300 Hz-3.4 kHz<br>±1 dB                                                           |

|                                        |                                                                                                                                                                                                                                          |                                                                                     | impedanc<br>maximum                                   |                                                 |                                                                                   |

| SYS_AUDIO_IN                           | 1000 mV RMS Max so 60 Sy im                                                                                                                                                                                                              |                                                                                     | Mini PCI (<br>source im<br>600 Ω, ma                  | pedance:                                        | 300 Hz-3.4 kHz<br>±1 dB                                                           |

|                                        |                                                                                                                                                                                                                                          |                                                                                     | System termination impedance: 50 k $\Omega$ , minimum |                                                 |                                                                                   |

| MOD_AUDIO_MON                          | Refer to the <i>PC Card Electrical Specification</i> , Section 5.2.12 for specification of the electrical characteristics of this signal                                                                                                 |                                                                                     |                                                       |                                                 |                                                                                   |

| AUDIO_GND                              | Connected to system board audio ground                                                                                                                                                                                                   |                                                                                     |                                                       |                                                 |                                                                                   |

| SYS_AUDIO_OUT_GND <sup>11</sup>        | Return signal for SYS_AUDIO_OUT. This may be used as a ground or may be used as a return for differentially receiving SYS_AUDIO_OUT. See Figure 4-1.                                                                                     |                                                                                     |                                                       |                                                 |                                                                                   |

| SYS_AUDIO_IN_GND <sup>11</sup>         | Return signal for SYS_AUDIO_IN. This may be used as a ground or may be used as a return for differentially receiving SYS_AUDIO_IN. See Figure 4-1.                                                                                       |                                                                                     |                                                       |                                                 |                                                                                   |

| VCC5VA <sup>11</sup>                   | 5 Volts ±5%, 100 mA maximum. Used primarily for voice circuit on modem card but may be used where quiet analog supply is needed. Voltage is supplied by system board to Type III Mini PCI Card. VCC5VA power return signal is AUDIO_GND. |                                                                                     |                                                       |                                                 |                                                                                   |

$<sup>^{11}</sup>$  Available on the system connector in the Type III form factor only.

<sup>&</sup>lt;sup>12</sup> Note: These signals are optional and are defined to provide convenient access to LAN signals without cabling. However, due to voltage limitations of the Type III connector, additional insulation or engineering will be required to meet IEEE 802.3 and 802.5 electrical isolation requirements.

### 4.1.1 Audio Interface Modes